国内首款Agentic AI自研EDA平台,合见工软发布智能体UDA 2.0重塑芯片设计范式

2026-03-18

中国数字EDA/IP龙头企业上海合见工业软件集团股份有限公司正式发布第二代数字设计AI智能平台——智能体UniVista Design Agent (UDA) 2.0。

雷娜科技破局“EDA最难堡垒” ——新一代逻辑综合工具实现数量级提速

2025-12-29

浙江雷娜科技有限公司作为国产电子设计自动化(EDA)领域的创新力量,隆重发布了两款重量级新品:逻辑综合工具升级版Raina Synth 3.0与静态时序签核工具Raina Time。

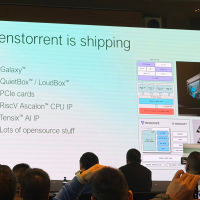

Tenstorrent宣布旗下TT-Ascalon™高性能RISC-V CPU正式上市

2025-12-04

RISC-V是一种开源指令集架构(ISA)规范,正在全球范围内被广泛采用,应用领域涵盖嵌入式系统到高性能计算。Ascalon的发布,标志着业界最高性能RISC-V CPU IP的诞生。

伴芯科技朱允山:AI智能体,重构EDA

2025-12-04

“我们既可以说是EDA公司,也可以不是EDA公司。”伴芯科技CEO 朱允山博士在接受《半导体制造》在内的媒体采访时表示,“我们聚焦的是大模型在芯片设计中的应用能力,而不是传统EDA公司做底层数据结构优化。我们正通过AI智能体推动Agentic EDA这一新范式。”

增速 29.4%!ICCAD-Expo 2025成功举办,中国 “芯” 力量加速崛起

2025-11-25

11月20日至21日,“2025集成电路发展论坛(成渝)暨三十一届集成电路设计业展览会”(简称ICCAD-Expo 2025)在成都中国西部国际博览城成功举办。

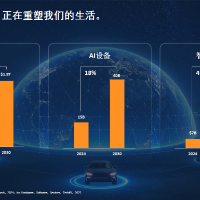

Ceva:以“AI Fabric”底座构建“物理AI”世界

2025-11-24

Ceva提出了“物理AI”的概念,人工智能深度融入并作用于物理世界的系统,它不仅仅是在云端的思考,更是在现实世界中的感知、决策和行动。