“计算机芯片正在实实在在地改变我们体验和与世界互动的方式——从我们如何连接到世界,到如何在数据中心提供计算,再到周围的自主系统,当然还有增强/虚拟现实。当今世界是处于一个了不起的时代。”Cadence高级副总裁兼系统验证事业部总经理Paul Cunningham博士在CadenceLIVE China 2025主会场开场白中说道。

半导体正在从“幕后”走向“前台”,系统公司已成为芯片设计的新生力量。小米、阿里巴巴、字节跳动、比亚迪等传统意义上的系统企业,正在基于用户体验和软件定义需求,进入芯片设计领域,掀起“软件定义芯片”的潮流。正如Paul Cunningham所言:“苹果成为全球最多产的芯片制造商之一,在20年前是令人惊讶的。”

在现场,他描绘了由AI驱动的半导体行业未来图景,并系统阐述了Cadence面向智能系统设计时代的“three-layer cake”战略,展现出EDA行业正从工具提供商向系统级设计和AI驱动自动化全面转型的大趋势。

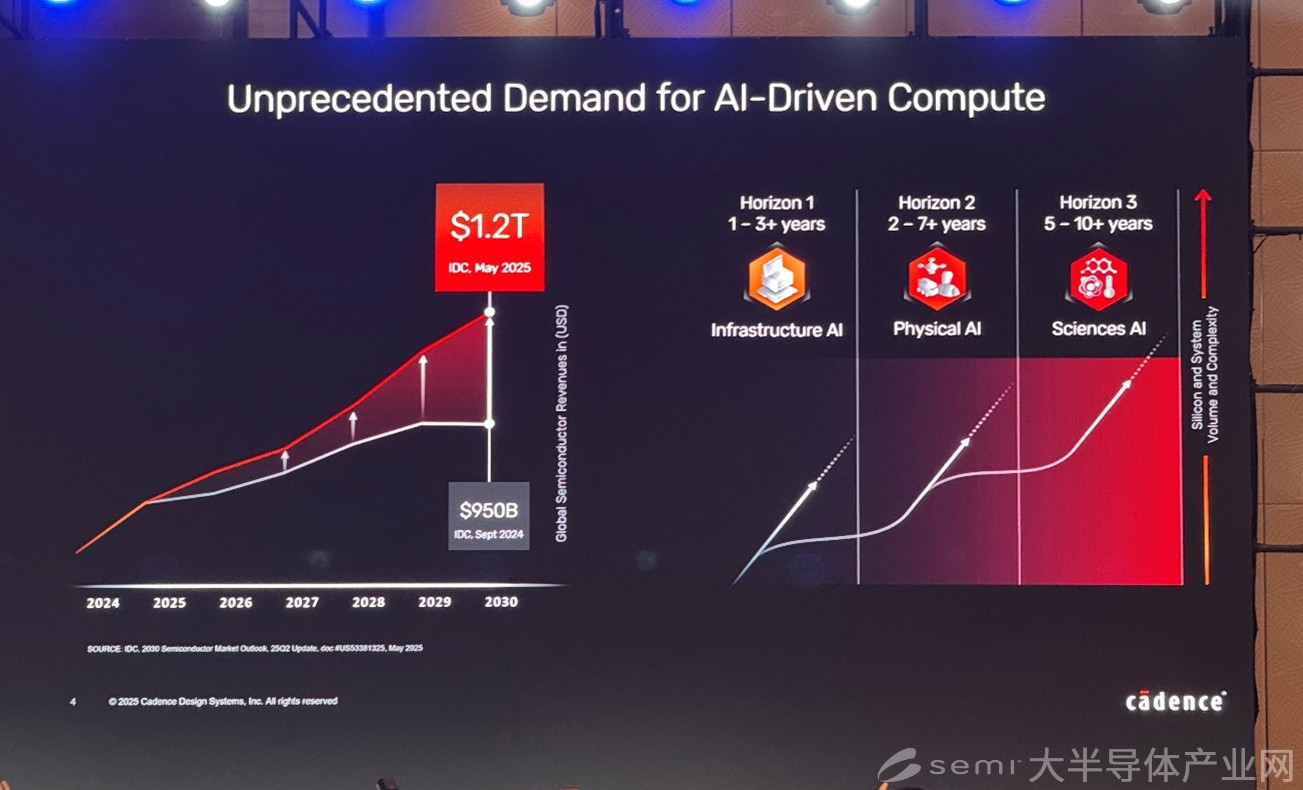

AI驱动半导体市场高速增长

人工智能以及围绕AI计算和基础设施正在发生的一切都令人震惊。仅一年时间,2030年半导体行业市场规模预测就从9000亿美元上修至超过1.2万亿美元,增幅近3000亿美元。Paul Cunningham认为,这一增长主要由数据中心AI计算的爆发式增长和边缘端AI部署所推动的。

他强调,这只是第一波浪潮,若将AI从数据中心溢出到边缘/汽车/机器人,再到AI+健康,市场规模还将进一步扩大。

“为了提供这种计算能力,从功耗的角度实现所需的效率,必须不断推动先进制程节点。”Paul Cunningham说道,为了实现这一点,数据中心AI领域的巨头们正在挑战半导体制造的极限。

以“three layer cake” 策略应对EDA行业三大挑战

随着芯片工艺迈向3nm、2nm甚至更先进节点,芯片设计复杂性呈指数级增长。晶圆厂制程节点的创建与工具的开发和所需IP的开发无法分离开来,需要协同工作。“我们需要将制程配方的调优与工具的选择、以及IP的开发结合起来,共同使其成为可能。”

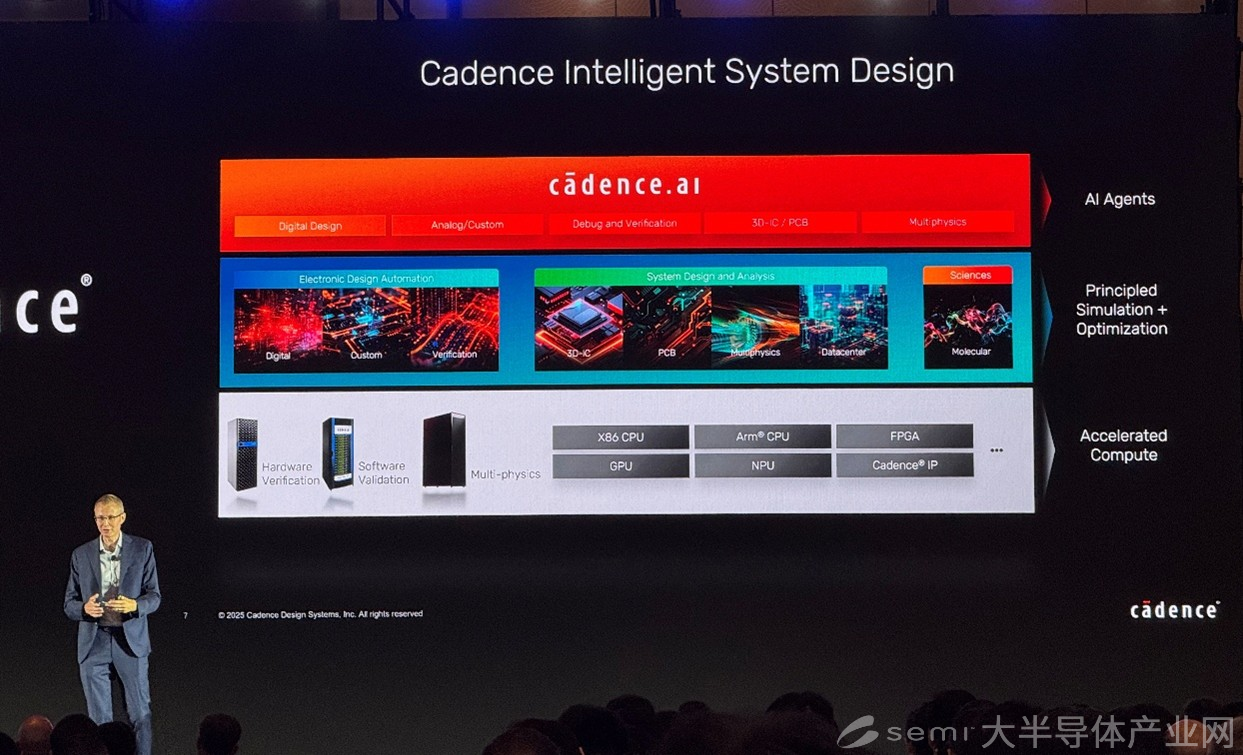

Paul Cunningham认为行业面临三大挑战:先进工艺节点的实现难度、多芯片封装带来的系统复杂性,以及从芯片到系统级的全流程优化需求。Cadence 提出的 “three layer cake” 模型精准概括了产业应对策略:

首先,从横向整合来看,Cadence从半导体本身扩展到先进封装、电路板和系统级设计,提供端到端解决方案。第二,从纵向融合的角度来看,Cadence结合基于原理的仿真优化与AI驱动方法,解决传统方法无法处理的复杂问题。第三是计算基础,采用异构计算架构,支持CPU、GPU和定制加速器,为复杂仿真提供算力支撑。

这一战略使Cadence能够提供从芯片到系统的全流程解决方案,特别是在3D-IC设计领域,其Integrity 3D-IC平台已实现超过100个流片案例,展现出强大的市场吸引力。

在加速仿真方面,Cadence最新的验证加速超级计算机Palladium Z3 搭载其全新自研的核处理器芯片,采取5纳米制程工艺,提供速度更快、预测能力更强的编译和全面的硅前硬件调试功能。与前一代产品相比,这款产品的容量增加超过2倍,速度快1.5倍,加快芯片和软件的协同验证,降低硬件仿真的部署成本,满足生成式AI、移动、汽车、超大规模和LLM应用的需求。

从数字孪生到物理孪生,EDA边界持续扩展

Paul Cunningham提出了一个颇具前瞻性的观点:传统EDA本质上是“半导体的数字孪生”,而Cadence正在将这一概念扩展到物理世界,创建“物理孪生”(Physical Twin)和“功能孪生”(Functional Twin)。

通过Physical Twin的产品组合,可以模拟整辆汽车进行碰撞测试,“以每小时60英里的速度驾驶装有假人的汽车撞墙,并通过计算完美模拟真实试验结果”。这种能力对于汽车、航空航天和生物医药等领域具有重要意义。

大型物理系统正日益由软件定义,平均来看,一辆现代汽车中的半导体价值正朝着超过1000美元的趋势发展,车内有数百颗甚至数千颗芯片,为了实际开发软件栈,以在不同车型中实现高质量大规模交付,需要虚拟的软件孪生体使开发者能够在实体硬件可用之前,就并行地进行软件开发、测试和集成工作,从而大幅缩短开发周期。

“这是Cadence加倍投入的领域。”Paul Cunningham说道,Cadence最近收购了VLAB Works和OpenEye,打造虚拟设备和制药领域的数字孪生。“随着在市场的不断扩展,physical twin和functional twin将变得越来越关键,因为我们正在迈向未来的软件定义系统。”

AI正在重构EDA工作流程

Cadence在AI领域的旅程始于2016年,当时DeepMind发布了AlphaFold,展示了传统强化学习技术、卷积循环神经网络等技术。“这使我们意识到可以在EDA工具内部使用机器学习,从而提升工具运行速度、结果质量与错误检出能力。”这就是Optimization AI(优化式AI),目前已以不同形式应用于产品中,用户甚至可能并未察觉其存在,因为其深度嵌入工具底层。

回顾Cadence及EDA行业过去四十年的发展,自动化与生产力提升始终是核心议题。通过不断提升设计抽象层级,我们实现了生产力质的飞跃——从手工绘制晶体管到晶体管级网表、标准单元、RTL的提出,再到System Verilog对RTL的抽象,乃至如今的高层次综合(允许用户直接编写C++程序并编译、综合、实现布局布线)。这种层层抽象与设计重用使我们能够应对包含2000亿晶体管的复杂设计。

然而,过去十年间,抽象层级的提升逐渐趋于平缓。当芯片源代码已近似于软件程序,还有哪些更高抽象层级可挖掘?

大语言模型(LLM)与生成式AI的出现使我们能够开始替代部分人类任务。用户可像与工程师对话一样与软件交流,软件也具备类人的推理能力。“我认为,未来的EDA不再仅仅是工具许可,更是‘虚拟人才’的许可,用户可从Cadence获得虚拟物理设计工程师、验证团队或版图团队。再结合核心引擎中的传统AI,代表了Cadence自动化的未来方向。”

根据调查数据,目前超过50%的Cadence工具使用已涉及优化式AI。预计随着生成式AI的全面部署,未来两年内这一比例将迅速突破80%。

为实现这一目标,Cadence建立了多个AI驱动解决方案平台:

• Cerebrus:AI数字设计平台,已助力超1000次流片;

• Verisium:AI数字验证平台,已部署于前20大客户中的18家;

• Virtuoso:定制设计平台;

• Optimality:系统级多物理场分析平台。

写在最后

Cadence致力于构建一个跨越所有工艺节点的完整设计IP组合,并在AI计算和数据中心领域提供领先节点支持。Paul Cunningham强调,我们将尽力与晶圆厂合作,并真正协同选择我们的工具,共同实现先进工艺节点的最佳性能。