当地时间2月26日,博通公司宣布,已开始向富士通交付业界首款基于其3.5D超大尺寸系统级封装(XDSiP)平台打造的2纳米定制计算SoC。博通高管称预计到2027年将至少售出100万颗基于该技术的芯片。

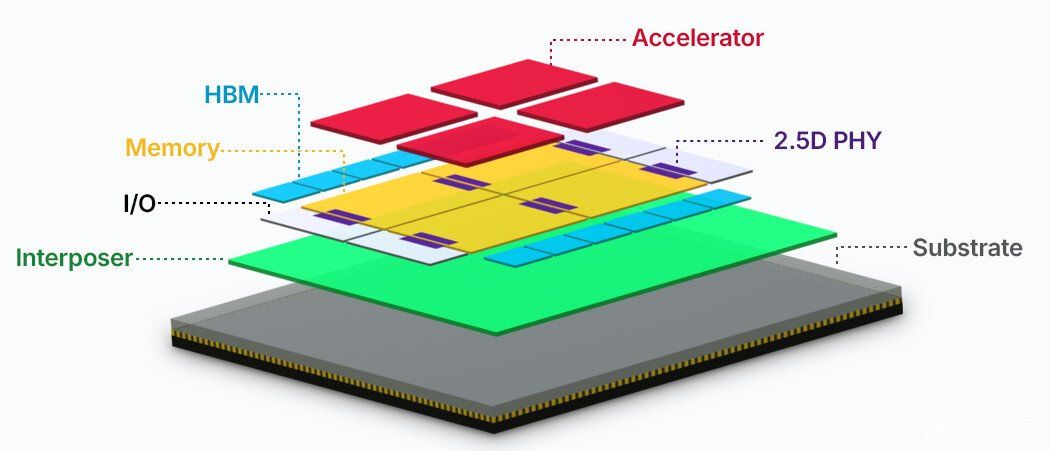

据了解,3.5D XDSiP是一个成熟的模块化多维堆叠芯片平台,结合了2.5D技术和采用面对面(F2F)技术的3D-IC集成,通过将多枚芯片上下堆叠并紧密结合,显著提升数据传输速度、降低延迟并优化能效。博通的XDSiP采用混合铜键合(Hybrid Copper Bonding, HCB)技术,针对芯片间面对面通信进行优化,能够实现更密集的电气接口,显著提高芯片间互连速度并缩短信号布线距离。

博通将3.5D XDSiP定位为下一代XPU的基础。借助该平台,消费级AI客户能够提供最先进的XPU,具备无与伦比的信号密度、卓越的能效和低延迟,以满足千兆瓦级AI集群的庞大计算需求。该平台的核心优势在于允许计算、内存和网络I/O在紧凑型态下独立扩展,实现高效率、低功耗的大规模计算。

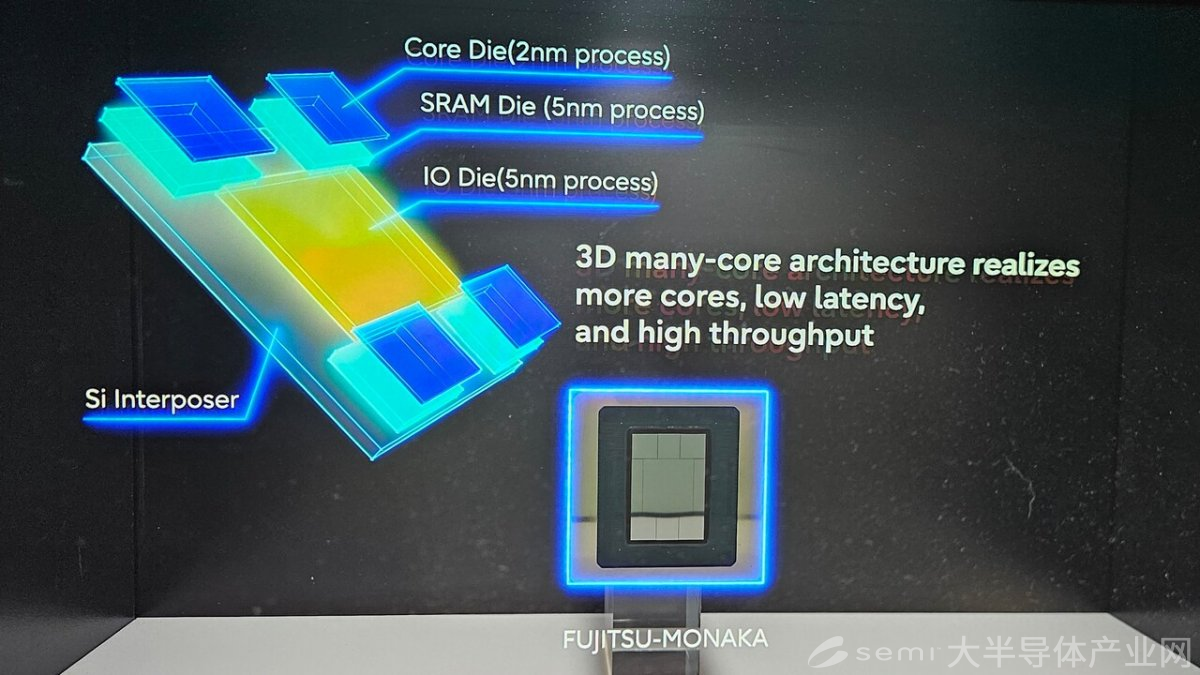

博通首位公开客户富士通(Fujitsu)已开始制作工程样片测试该设计,并计划于今年晚些时候量产这种堆叠式芯片。富士通正在利用3.5D XDSiP技术开发其FUJITSU-MONAKA数据中心处理器,该芯片由台积电采用最先进的2纳米工艺制造计算核心,并与一枚5纳米工艺的SRAM芯片进行融合封装。

而根据博通的芯片设计路线图显示,预计今年下半年将再推出两款基于堆叠技术的产品,并计划在2027年再提供三款样片。目前约有六款设计正在推进中,其中约80%是搭载HBM显存的XPU方案。