半导体存储器的发展背景

世界上最早的全电子化存储器是1947年在曼彻斯特大学诞生的威廉姆斯-基尔伯恩管 (Williams-Kilburn tube),其原理是用阴极射线管在屏幕表面上留下记录数据的“点”。从那时起,计算机内存开始使用磁存储技术并经历了数代演变,相关系统包括磁鼓存储器、磁芯存储器、磁带驱动器和磁泡存储器。从1970年代开始,主流的集成半导体存储器则主要分为三类:动态随机存取存储器 (DRAM)、静态随机存取存储器 (SRAM) 和闪存。

计算机内存主要是DRAM和SRAM。二者相比,DRAM的存储密度更高,而SRAM则具有最快的片上缓存。这两类半导体存储器都已经历了数十年的发展。DRAM需要周期性刷新才能保持住存储的数据,它的发展主要受存储密度和成本的影响。SRAM不需要周期性刷新就能锁存“0”和“1”信号,影响其发展的主要因素则是单元面积和读取速度。

DRAM技术衍生自早前的随机存取存储器 (RAM)。在DRAM出现之前,RAM是大家比较熟悉的存储器形态,其特点是只能保存正在读/写的数据,一旦关机断电就会擦除所有内存。最早的RAM系统由复杂的电线和磁铁组成,体积庞大且耗电量大,基本不具备实用性。IBM的罗伯特·丹纳德 (Robert Dennard) 改变了这一情况,他发明了使用单个晶体管和存储电容器的RAM存储单元。正是基于他的这项杰出发明,我们才逐渐发展出了在现代计算机中能容纳十亿个甚至更多RAM单元的单芯片。

半导体存储器面临的挑战及应对办法

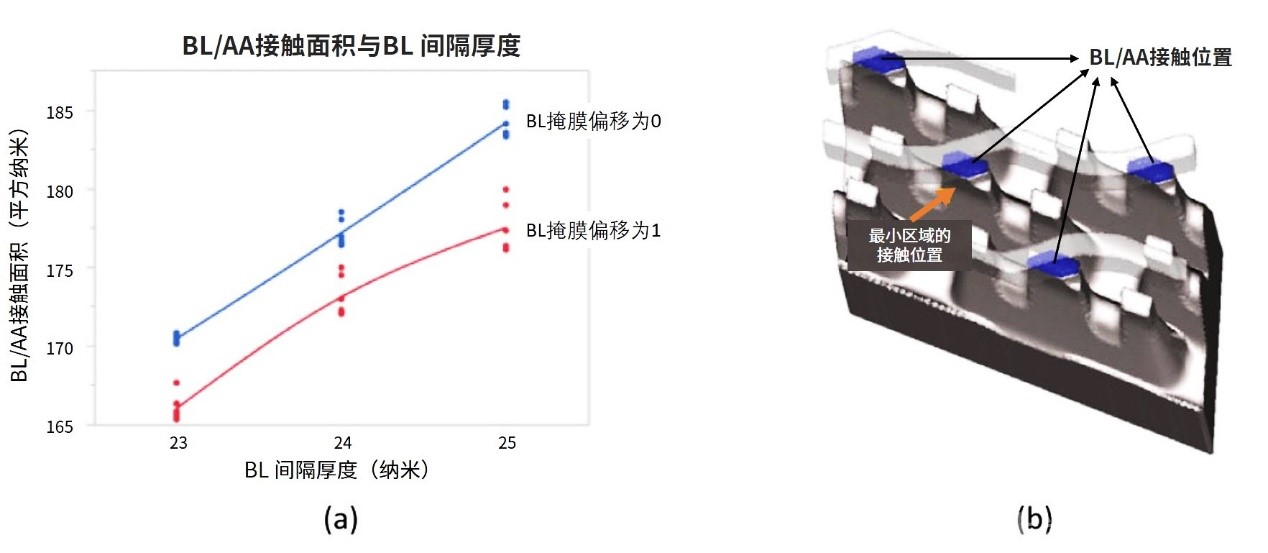

如今,DRAM技术的发展面临很多和CPU相同的挑战,包括多重图形化、邻近效应和存储节点泄漏等。DRAM的开发需要精确的建模才能预测前述问题的影响并做相应的优化来避免良率受损。举例来说,在确定位线 (BL) 到有源区 (AA) 接触面积时就必须特别注意位线芯轴间隔和掩膜偏移,稍有疏忽就可能导致良率问题。

仅依靠基于晶圆的实验很难找出晶圆级失效的原因并确定与之相关的工艺参数。在工艺变化研究中制造测试晶圆并测量晶圆上的最终接触面积,费时且成本较高。先进的工艺建模技术能帮我们解决前述问题。通过对BL间隔层厚度变化和BL掩膜位移同时建模,基于DoE(实验设计)统计变化研究,可以确定最小接触区域。基于前述研究的结果,结合自带的结构搜索/DRC功能就可以确定具体芯片上的最小接触位置和区域。SEMulator3D®就是一个能完成上述研究的工艺建模平台。基于该平台的工艺变化研究能够帮助我们发现与BL芯轴间隔厚度和掩膜转换相关的潜在问题。图1 (a) 展示的就是用SEMulator3D检查BL间隔厚度和掩膜转换对BL/AA接触面积的影响,而图1 (b) 则显示了最小接触区域在芯片上的位置。

图1. (a) BL/AA接触面积与BL间隔厚度和掩膜偏移的关系;(b) 最小接触区域及其位置。

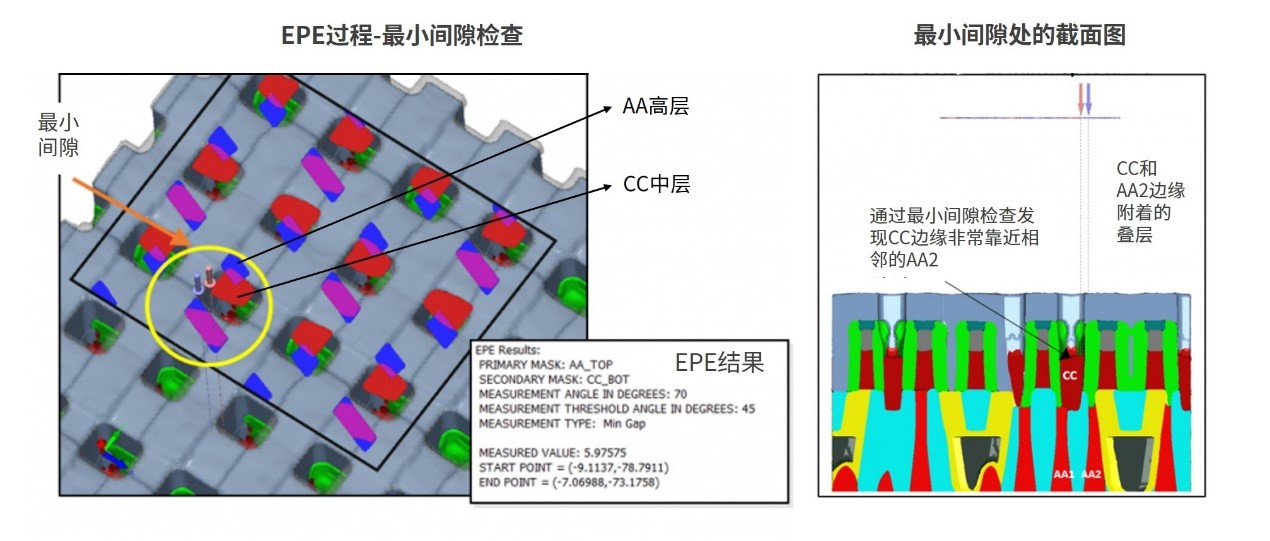

DRAM工艺开发还要注意存储节点与相邻有源区的距离,因为过度接近会导致设备短路。一旦发生短路,其背后的根本原因很难确定。但不解决的话,这些问题到了开发后期可能导致严重的可靠性与良率问题。若能在试产之前通过准确地建模确定电容器触点与AA在不同z位置的最小间隙,我们就有可能避免前述的严重后果。图2展示的是在工艺建模过程中确定的BL到AA接触区域,其中高亮部分就是需要通过工艺或设计变更解决的最小间隙问题。通过图中示例可以看出工艺步骤之间复杂的相互影响并最终影响到DRAM的可靠性和良率,因此通过准确的建模来确定这些影响是很有意义的。

图2. 晶圆制造工艺的虚拟建模 (SEMulator3D),图中展示的存储节点触点与AA之间可能存在短路。

支持多次擦除和重复编程的闪存出现于1984年,目前它已被用于各种消费类设备、企业系统和工业应用的存储和数据传输。闪存可以长期保存数据,即使关机断电也不受影响,其制造技术目前已经从2D转向3D(即3D NAND),以增加存储密度。

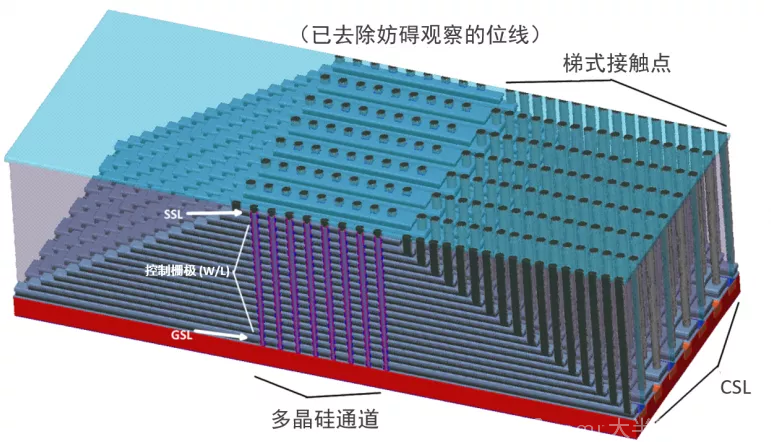

单层3D NAND结构的刻蚀非常复杂,因为高深宽比必须在一组交替的材料中刻蚀,同时还要避免刻蚀孔发生弯曲和倾斜,并且需要专门刻蚀出用来分离相邻存储单元的“狭缝”。完整3D NAND结构的刻蚀甚至要更复杂一些,因为其中还包含了形成字线 (WL) 触点所必需的“梯式”刻蚀。图3展示的是用SEMulator3D建模的完整3D NAND阵列,可以看出最先进的3D NAND存储器结构相当复杂,而且这还只是单层结构。

图3. 使用SEMulator3D建模的单层3D NAND存储单元。

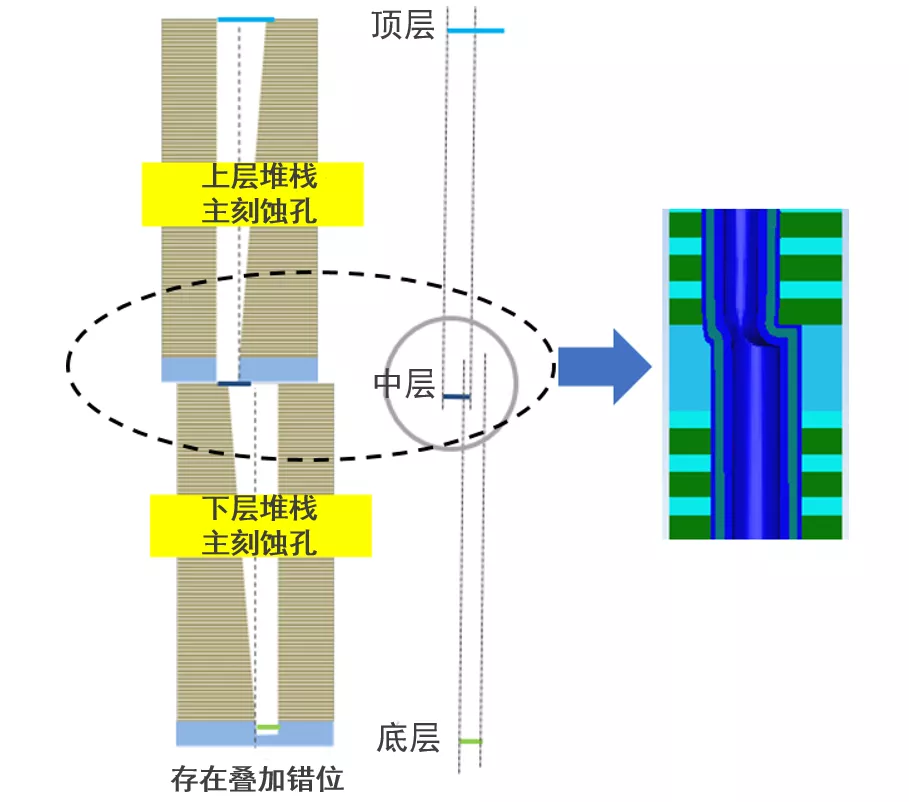

工艺的复杂性在2D向3D闪存结构的过渡中急剧提升,原因在于3D结构需要多层沟道的刻蚀。当今的大多数3D NAND存储器都有两层,这就意味着可能出现顶层与底层错位问题。图4展示的就是多层3D NAND沟道刻蚀面临的问题和挑战。

图4. SEMulator3D输出结果,其中展示的是层错位问题和其导致的沟道刻蚀偏移。

这就是层错位和其导致的沟道刻蚀偏移。这种错位可能是工艺差异导致的,并且是任何3D NAND工艺开发都绕不开的问题。从图中示例可以看出,层与层之间的一致性对多层3D NAND存储单元的结构质量有非常重大的影响。和DRAM的情况一样,我们可以在SEMulator3D系统中针对3D NAND的层错位问题做DoE统计变化研究,且只需要根据分析结果采取纠正措施即可,无需再花费时间和金钱去进行晶圆测试。